## **TABLE OF CONTENTS**

| General Chair's Welcome | 2              |

|-------------------------|----------------|

| Sponsors                | 3              |

| Important Information   |                |

| Welcome to San Diego    |                |

| Keynotes                | 6,7,10,11      |

| Awards                  | 8,9            |

| Management Day          | 12             |

| ESS Executive Day       |                |

| Technical Sessions      | 14-31          |

| User Track              | 33-38          |

| Monday Tutorials        | 40,41          |

| Workshops               | 42-45          |

| Work-in-Progress (WIP)  | 46,47          |

| Colocated Events        | 48-51          |

| Pavilion Panels         | 52-56          |

| Adjunct Events          | 57             |

| Additional Meetings     | 58,59          |

| Exhibitor Forum         | 60-64          |

| Event Schedule          | Center Foldout |

| Exhibit Floor Plan      | Center Foldout |

| Exhibitor List          | 66,67          |

| Exhibiting Companies    | 70-115         |

| Exhibition Highlights   | 102            |

| Supplemental Listing    | 116            |

| Committees              | 120-127        |

| Index                   | 128            |

## **GENERAL CHAIR'S WELCOME**

### SEE YOU AT THE NEW DAC!

### **DEAR COLLEAGUE:**

It is a great pleasure to welcome you to the 48th edition of the Design Automation Conference in San Diego. In the age of web-conferencing DAC is changing its format to provide the maximum opportunity for multi-way interaction at the conference. In addition to the kickoff reception on Sunday, DAC will feature a reception at the end of each day to stimulate intermingling of all DAC participants from the exhibit floor to the technical sessions. In the technical program, all paper presentations are shortened and immediately followed by a poster session where a dialogue can take place between the author and the audience. At the Wednesday reception the Work In Progress (WIP) session will take place. This new initiative will provide a forum for new ideas, not yet fully ready for a publication, to be exchanged with other experts in the field.

DAC features four keynotes this year. On Monday afternoon we will kick-off with an "Up Close and Personal" with Steve Wozniak. On Thursday we will close the keynote series with a look at the future of computing. Dharmendra S. Modha, IBM, will describe a project to build brain-like cognitive computing chips that scale to human cortex.

DAC is dramatically increasing its focus on Embedded Systems and Software (ESS). On Tuesday Lisa Su, Freescale Semiconductor, will discuss the megatrends that drive Embedded Multi-Core Innovation. Her keynote will outline the evolution of embedded multicore processing solutions that are increasingly enabling the device and infrastructure markets. On Wednesday, Gadi Singer, Intel Corp., will comment on ESS impact on the EDA industry. His keynote will highlight opportunities for innovation and the changes necessary to support this brisk evolution and value creation in electronic systems. Wednesday will feature an ESS Executive day, to provide managers with timely information to help them make decisions where business and technology in ESS domain intersect. More than 30% of the technical program, special sessions and panels are focused on Embedded Systems and Software.

DAC will feature a vibrant exhibition showcasing nearly 200 companies, including all of the largest EDA vendors and significant foundries. At the exhibition we will have a special ESS Zone and IP SOC Pavilion.

DAC has changed the tutorial format. Each tutorial participant can now select three two-hour courses from an exciting collection of six tutorials. All tutorials will take place on Monday this year.

DAC's Technical Program Committee (TPC) has worked hard to present an outstanding technical program this year. The TPC selected 156 papers of the 690 submissions (23% acceptance) for presentation in 4 parallel tracks, covering the entire gamut of topics including Embedded Systems & Software, front-end, back-end, and test. A separate Special Session track will present hot topics and emerging technologies. An exciting set of panels will address topics covering a broad range of Embedded Systems & Software, EDA and emerging areas. Finally, the DAC technical program continues to extend the User Track. This program, specifically designed for EDA tool users, features presentations and poster sessions that highlight outstanding solutions to critical design and methodology challenges, and case studies of innovative tool use.

The number of DAC workshops has almost doubled to eleven. A new all-inclusive registration package will give you access to all of them. Topics range from Smart Grid, Cloud computing and Parallel Algorithms to Inter Vehicle Networking.

An impressive constellation of 12 colocated events complements the DAC program: this includes established conferences and symposia such as AHS, CELUG, DFM&Y, HOST, IWBDA, IWLS, NANOARCH, SASP, and SLIP as well as events focusing on PDKs and OpenAccess scripting.

As organizers of the event, we work with DAC's sponsors and hundreds of volunteers to make it worth your time to attend. I am looking forward to see you all at DAC in San Diego, June 5-9!!

LEON STOK GENERAL CHAIR, 48<sup>TH</sup> DAC

### SPONSORS

ACM, the Association for Computing Machinery, is the world's largest educational and scientific computing society, uniting computing educators, researchers and professionals to inspire dialogue, share resources and address the field's challenges. ACM strengthens the computing profession's collective voice through strong leadership, promotion of the highest standards, and recognition of technical excellence. ACM supports the professional growth of its members by providing opportunities for life-long learning, career development, and professional networking. www.acm.org

The ACM Special Interest Group on Design Automation has a long history of supporting conferences and the EDA profession. In addition to sponsoring DAC, SIGDA sponsors ICCAD, DATE, and ASP-DAC plus approximately 15 smaller symposia and workshops. SIGDA provides a broad array of additional resources to our members, to students and professors, and to the EDA profession in general. SIGDA organizes the University Booth and Ph.D. Forum at DAC, and the CADathlon at ICCAD, and also funds various scholarships and awards. Other benefits provided to SIGDA members include the SIGDA's E-Newsletter containing information on upcoming conferences and funding opportunities, SIGDA News highlighting most relevant events in EDA and semiconductor industry, and the "What is...?" column that brings to the attention of EDA professionals the most recent topics of interest in design automation. For further information on SIGDA's programs and resources, see http://www.sigda.org.

### **IEEE/COUNCIL ON ELECTRONIC** DESIGN AUTOMATION

The IEEE is the world's leading professional association for the advancement of technology, with 400,000 members across 160 countries. The IEEE Council on Electronic Design Automation (CEDA) provides a single focal point for all EDA activities across six major IEEE societies (Circuits & Systems, Computer, Electronic Design Provided Research Electron Devices, Solid State Circuits, Antennas & Propagation, and Microwave Theory & Techniques). The Council sponsors or co-sponsors over a dozen key EDA conferences, including the Design Automation Conference (DAC), and the International Conference on Computer Aided Design (ICCAD), Design Automation and Test in Europe (DATE) and events at Embedded Systems Week (ESWeek). The Council also publishes the IEEE Transactions on CAD, as well as the IEEE Embedded Systems Letters, and sponsors active technical committees like the DATC and CANDE. Since its founding, the Council has expanded its support of emerging areas within EDA such as nanoscale systems, sponsored new initiatives including the Distinguished Speaker Series and is increasing recognition of members of the EDA profession via awards such as the A. Richard Newton Award, Phil Kaufmann Award, and Early Career Award. The Council welcomes new volunteers and local chapters. For more information on CEDA, visit: www.c-eda.org.

### EDA CONSORTIUM

The EDA Consortium (EDAC) is the international association of companies that provide tools and services enabling engineers to create the world's electronic products. EDAC addresses issues that are common to its members and the community they serve. Recent accomplishments include simplification of international EDA export regulation, coordinating software anti-piracy efforts, a quarterly Market Statistics Service (MSS) report, and publication of an industry Operating Systems Roadmap. Companies that become EDAC members are eligible for a 10% discount on DAC Exhibit Booth and Suite Space. Contact the EDA Consortium today about sponsorship and membership opportunities. For more information on the EDA Consortium, visit: www.edac.org.

### IMPORTANT INFORMATION

### **EXHIBIT HOURS**

**LOCATION** Halls D - H

**HOURS**

Monday, June 6 9:00am - 6:00pm Tuesday, June 7 9:00am - 6:00pm Wednesday, June 8 9:00am - 6:00pm

### REGISTRATION

**LOCATION** Lobby D

**HOURS**

Sunday, June 5 7:30am - 6:00pm Monday, June 6 - Thursday, June 9 7:00am - 6:00pm

### **INFORMATION DESK**

The Information Desk will be located in the Lobby D of the San Diego Convention Center. Dial (619) 525-6203.

### **FIRST AID ROOM**

The First Aid Room is located in Lobby D of the San Diego Convention Center. For assistance, call ext. 5490; for an emergency, call ext. 8080. A nurse will be on duty at all times while meetings and exhibits are open. Dial (714) 765-8950.

Help may be reached 24 hours a day from any house phone within the San Diego Convention Center.

### **48TH DAC PROCEEDINGS DVD**

Additional copies of the 48th DAC Proceedings DVD may be ordered prepaid from:

ACM Order Department Sponsored by:

ACM Order Department

P.O. Box 11414, New York, NY, 10286-1414 Phone: +1-800-342-6626 (US and Canada)

Phone: +1-212-626-0500 (Global)

Fax: +1-212-944-1318 (all other countries)

email: orders@acm.org

### STAY CONNECTED AT DAC

**WIRELESS INTERNET**

Sponsored by:

DAC is offering complimentary wireless internet throughout the San Diego Convention Center. Look for SSID: DAC2011.

### **MOBILE DEVICES**

DAC has a special website built for access from handheld mobile devices. From your smartphone, featurephone, or tablet log in to www.dac.com and you will be automatically redirected to the mobile site. Presentation schedules, the exhibitor listing and other useful information are available and optimized for viewing on small screens.

### DAILY UPDATES ON DAC.COM

Check the DAC website daily for a complete listing of each day's schedule, the latest exhibitor announcements, and press coverage.

**FOOD COURT**

Sponsored by:

**SYNOPSYS**

The food court is located in Hall G on the exhibit floor and includes tables with power connections for laptop plug-in.

### **DACNET - 2011**

DACnet internet stations are available on the 2nd level by room 33 and on the exhibit floor in the food court.

### "BIRDS-OF-A-FEATHER" MEETINGS

DAC will provide conference rooms for informal groups to discuss items of common technical interest. These very informal non-commercial meetings, held after hours, are referred to as "Birdsof-a-Feather" (BOF). All BOF meetings are held at the San Diego Convention Center, Tuesday, June 7 / 7:00 - 8:30pm. To arrange a BOF meeting, please sign up at the Information Desk located in Lobby D. A meeting room will only be assigned if ten or more people sign up. An LCD projector and screen will be provided. Check DACnet and the Birds-of-a-Feather board at the Information Desk.

### ACCESS THE CONFERENCE PROGRAM WITH A QR CODE:

### **WELCOME TO SAN DIEGO!**

### **SAN DIEGO ATTRACTIONS**

San Diego has many world famous attractions. From the San Diego Zoo, to Sea World, to the many natural wonders this city has to offer, there is always something fun and exciting to see and do! Within walking distance of the Convention Center is San Diego's Gaslamp Quarter. This National Historic District features many dining options, shopping and premier entertainment.

### **WEATHER**

San Diego has beautiful weather year round and has an average temperature of 71 degrees. There is no typical day in San Diego, due to the topography of the location. You may experience anything from coastal, mountain and desert environments, just in one day! Days in San Diego are sunny and evenings are pleasingly cool, so be sure to bring a light jacket. With an average of 300 sunny days per year, you are sure to have a great day while in San Diego!

### VISIT WWW.SANDIEGO.ORG FOR MORE INFORMATION

or call the San Diego Convention and Visitors Bureau at (619) 232-3101.

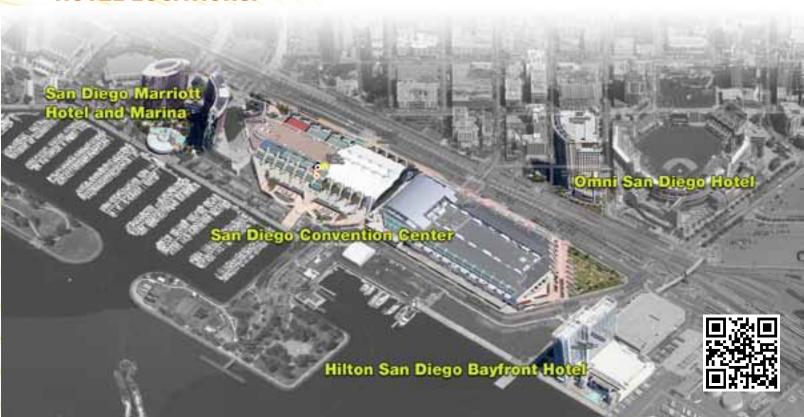

### **HOTEL LOCATIONS:**

## **MONDAY KEYNOTE**

June 6

Room: 20AB

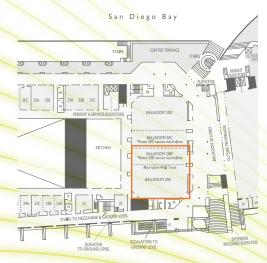

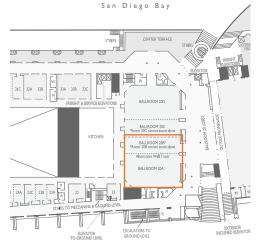

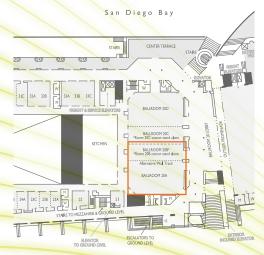

San Diego Bay

STARS CONTENTERACE STARS

GENTER TERRACE

STARS TO MEZZAMINE & GOUNG LEGE

STARS TO

2:00 - 3:00pm

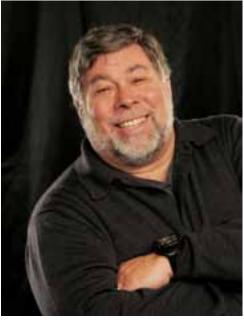

## UP CLOSE AND PERSONAL WITH STEVE WOZNIAK

### **STEVE WOZNIAK**

Fusion-io. San Jose. CA

### **SUMMARY:**

Steve Wozniak will be interviewed live on stage by San Jose Mercury News columnist Mike Cassidy on a wide range of topics, including the 'joy' of engineering and following your passion to convert innovative ideas into reality. Steve will provide a unique insight into the vision that started the largest and most successful technology company in the world.

### BIO:

A Silicon Valley icon and philanthropist for more than thirty years, **Steve Wozniak** has helped shape the computing industry with his design of Apple's first line of products the Apple I and II and influenced the popular Macintosh. In 1976, Wozniak and Steve Jobs founded Apple Computer, Inc. to market Wozniak's Apple I personal computer. For his achievements at Apple Computer, Inc., Wozniak was awarded the National Medal of Technology, the highest honor bestowed on America's leading innovators.

Since the 1980's, Wozniak has been involved in various business and philanthropic ventures. He has spent a great deal of time and energy focusing on computer usage in schools by stressing hands-on learning and encouraging creativity for students. In 2000, he was inducted into the Inventors Hall of Fame and was awarded the prestigious Heinz Award for Technology, the Economy and Employment. Wozniak also co-founded the Electronic Frontier Foundation, and was the founding sponsor of the Tech Museum, Silicon Valley Ballet and Children's Discovery Museum of San Jose. He currently serves as Chief Scientist for Fusion-io.

## **TUESDAY KEYNOTE**

June 7

8:30 - 10:00am

# MEGATRENDS DRIVING EMBEDDED MULTICORE INNOVATION

Room: 20AB

### **LISA SU**

Freescale Semiconductor, Inc., Austin, TX

### **SUMMARY:**

Internet traffic is dramatically increasing, and the fastest growing segment, mobile network traffic, is expected to double every year for the next five years. In the next decade, more than twenty billion smart mobile devices will be connected to the Internet. This exponential growth is requiring new innovation throughout embedded devices and the supporting infrastructure to keep pace with the growing demand.

This talk will outline the evolution of embedded multicore processing solutions that are increasingly enabling the device and infrastructure markets. Topics covered will include the evolution of the network infrastructure, growth of multi-purpose embedded devices, increased trend towards heterogeneous system-on-chip (SOC) integration, balanced with the market realities of maintaining system development costs and energy efficiency. Continued innovation in every part of the value chain is needed in hardware design, software design, and in EDA tools. Key solutions and challenges for embedded multicore designs will be discussed as we move to advanced geometries and more highly integrated SOCs.

### BIO:

**Lisa Su** is the senior vice president and general manager of networking and multimedia for Freescale Semiconductor.

Lisa joined Freescale in June 2007 as chief technology officer to lead Freescale's technology roadmap and global research and development (R&D) operations. She was named general manager of networking and multimedia in September 2008.

Prior to joining Freescale, Lisa was at International Business Machines Corporation (IBM), where she was vice president of the Semiconductor Research and Development Center and responsible for the strategic direction of IBM's silicon technologies, joint development alliances and semiconductor R&D operations. Lisa joined IBM in 1995 and held various engineering and business management positions including vice president of technology development and alliances in the IBM Systems and Technology Group and director of the PowerPC Product Line. Prior to IBM, Lisa was a Member of Technical Staff at Texas Instruments. She has extensive experience in the semiconductor industry leading technology innovation, microprocessor development and the launch of new products.

Lisa has authored or co-authored more than 40 technical publications and co-authored a book chapter on next-generation consumer electronics. She was named in MIT Technology Review's Top 100 Young Innovators in 2002 and was named Fellow of the IEEE in 2009. Lisa received bachelor's, master's and doctorate degrees in electrical engineering from the Massachusetts Institute of Technology.

### **GENERAL SESSION**

Room: 20AB

### **OPENING REMARKS**

Leon Stok - 48th DAC General Chair

### **AWARDS PRESENTATIONS**

### **KEYNOTE ADDRESS**

MEGATRENDS DRIVING EMBEDDED MULTICORE INNOVATION

Lisa Su - Vice President and General Manager of Networking and Multimedia for Freescale Semiconductor

### **AWARDS**

### MARIE R. PISTILLI WOMEN IN EDA A. RICHARD NEWTON GRADUATE **ACHIEVEMENT AWARD**

Limor Fix - Senior Principal Engineer, Director of Academic Programs and Research (ARP), Intel Corp., Hillsboro, OR

For her significant contributions in helping women advance in the field of EDA technology.

### P.O. PISTILLI UNDERGRADUATE **SCHOLARSHIPS FOR ADVANCEMENT IN COMPUTER SCIENCE AND ELECTRICAL ENGINEERING**

The objective of the P.O. Pistilli Scholarship program is to increase the pool of professionals in Electrical Engineering, Computer Engineering, and Computer Science from under-represented groups (women, African-American, Hispanic, Native American, and physically challenged). In 1989, ACM Special Interest Group on Design Automation (SIGDA) began providing the program. Beginning in 1993, the Design Automation Conference provided the funds for the scholarship and a volunteer committee continues to administer the program for DAC. DAC normally funds a \$4000 scholarship, renewable up to five years, to graduating high school

The 2011 recipient is:

Mario Morales

### **SCHOLARSHIPS**

Each year the Design Automation Conference sponsors the A. Richard Newton Graduate Scholarship to support graduate research and study in Design Automation (EDA). Each scholarship is supported and study in Design Automation (EDA). is awarded directly to a University for the Faculty Investigator to expend in direct support of the project and students named in the application. The criteria are: the quality and applicability of the proposed research; the impact of the award on the EDA program at the institution; the academic credentials of the student(s); and financial need.

This year's scholarship goes to:

Advisor: Prof. Ayse K, Coskun - Boston Univ., Boston, MA

Student: Jie Meng - Boston Univ., Boston, MA

Project: 3D Systems for Low-Power High-Performance Computing

### 2010 PHIL KAUFMAN AWARD FOR DISTINGUISHED **CONTRIBUTIONS TO EDA**

Sponsored by the EDA Consortium and IEEE Council on EDA

P.O. (Pat) Pistilli - Chairman MP Associates, Inc.

Pat Pistilli is honored for his pioneering the electronic design automation (EDA) industry and building the Design Automation Conference (DAC) as its premiere showcase and networking platform.

### IEEE CEDA OUTSTANDING SERVICE CONTRIBUTION

For significant services as DAC General Chair 2010 Sachin Sapatnekar - Univ. of Minnesota, Minneapolis, MN

## **GENERAL SESSION**

### **AWARDS**

## DONALD O. PEDERSON BEST PAPER AWARD FOR THE IEEE TRANSACTION ON CAD:

A. Singhee and R. A. Rutenbar

**For Paper Titled:** "Statistical Blockade: Very Fast Statistical Simulation and Modeling of Rare Circuit Events and Its Application to Memory Design,"

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 28, No. 8, pp. 1176-1189, August 2009.

### ACM/IEEE A. RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

For pionieering work on technology mapping for FPGA that has made significant impact to the FPGA research community and industry.

"FlowMap: an optimal technology mapping algorithm for delay optimization in lookup-table based FPGA designs"

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, January 1994, Vol. 13, Issue 1. Pages 1-12.

#### Authors:

Jason Cong - *Univ. of California, Los Angeles, CA* Yuzheng "Eugene" Ding - *Xilinx Inc., Longmont, CO*

### ACM TRANSACTIONS ON DESIGN AUTOMATION OF ELECTRONIC SYSTEMS (TODAES) 2011 BEST PAPER AWARD

For Paper Titled: "Cost minimization while satisfying hard/soft timing constraints for heterogeneous embedded systems"

TODAES Vol 14, No 2, Article 25, April 2009.

Authors: Meikang Qiu and Edwin H.-M. Sha

The Award recognizes the best paper published in the ACM Transactions on Design Automation of Electronic Systems in the time window from the April 2008 issue to the January 2011 issue.

### SIGDA OUTSTANDING NEW FACULTY AWARD

Farinaz Koushanfar - Rice Univ.

For her pioneering research in the areas of secure, robust, and sustainable computing.

### SIGDA OUTSTANDING PHD DISSERTATION AWARD

Nishant Patil - Stanford Univ., Palo Alto, CA

For the dissertation titled "Design and Fabrication of Imperfection-Immune Carbon Nanotube Digital VLSI Circuits," advised by Prof. Subhasish Mitra.

### 2011 STUDENT DESIGN CONTEST WINNING ENTRIES

A 90nm CMOS Data Flow Processor using Fine Grained DVS for Energy Efficient Operation from 0.3V to 1.2V

S. Arrabi, Y. Shakhsheer, K. Craig, S. Khanna, J. Lach, and B. H. Calhoun - *Univ. of Virginia*

A 1900MHz-Band GSM-Based Clock-Harvesting Receiver with -87dBm Sensitivity

Jonathan K. Brown and David D. Wentzloff - Univ. of Michigan

SRAM Dynamic Stability Characterization Using Pulsed Word-lines in 45nm CMOS

Seng Oon Toh and Borivoje Nikolic - Univ. of California

Design and Implementation of Centip3De, a 7-layer Many-Core System

David Fick, Ronald G. Dreslinski, Bharan Giridhar, Gyouho Kim, Sangwon Seo, Matthew Fojtik, Sudhir Satpathy, Yoonmyung Lee, Daeyeon Kim, Nurrachman Liu, Michael Wiekowski, Gregory Chen, Trevor Mudge, Dennis Sylvester, and David Blaauw - *Univ. of Michigan*

A Flexible Wireless Receiver System with a 7b 21 MS/s Filtering SAR ADC

David T. Lin, Li Li, John Bell, Ming-Hao Wang and Michael P. Flynn - Univ. of Michigan

Augmented Reality Headset based on a Heterogeneous Multi-core Object Recognition Chip

Seungjin Lee, Jinwook Oh, Junyoung Park, Joonsoo Kwon, and Hoi-Jun Yoo - *KAIST*

A 0.9-V 11-bit 25-MS/s 0.58-mW Binary-Search SAR ADC in 90-nm CMOS

Ying-Zu Lin, Ya-Ting Shyu, Guan-Ying Huang, Chun-Cheng Liu and Soon-Jyh Chang - *National Cheng Kung Univ.*

A Video Stabilization System with Background Motion Estimation and Smoothing for Digital Camera

Chih-Lun Fang, Hui-Min Chuang and Tsung-Han Tsai - National Central Univ.

### **WEDNESDAY KEYNOTE**

June 8

11:00am - 12:00pm

## THE IMMINENT EDATRANSFORMATION

### **GADI SINGER**

Intel Corp., Santa Clara, CA

### **SUMMARY:**

The EDA industry faces a substantial shift. Electronic systems are going through fundamental and rapid change in domains ranging from TVs and in-vehicle devices to phones, tablets, and even PCs. These new systems require unprecedented connectivity, hardware and software complexity, and application and user interactions. To meet these challenges, the EDA industry must evolve and expand quickly to enable highly interdependent silicon, software, system, and experience solutions. The EDA industry's current offering needs to be reassessed, and the scope of the industry's capabilities and environments needs to encompass exploration, design, verification, and debug across the complete hardware and software stack. This keynote will highlight opportunities for innovation and the changes necessary to support this brisk evolution and value creation in electronic systems.

Room: 20AB

### BIO:

**Gadi Singer** is vice president of the Intel Architecture Group and General Manager, SOC Enabling Group for Intel Corporation. The SOC Enabling Group is responsible for delivering central building blocks and driving Intel's SOC silicon design and software development capabilities focusing on fast turnaround time and modularity practices. Singer joined Intel in 1983, holding a variety of senior technical and management positions. He was appointed VP in 1999 and CTO of Intel Communications Group in 2004, among other accomplishments.

From 2005 through 2007, Singer served as General Manager of the Ultra Mobility Group. Among his prior roles, Singer was GM of Intel's Design Technology Division, co-GM of the IA-64 Processor Division and GM of Enterprise Processors Division. Singer received three Intel Achievement Awards for his technical contributions. He was Chairman of EDA Industry Council from 1997 to 1999. Singer is alumnus of the Technion, Israel.

## THURSDAY KEYNOTE

June 9

11:00am - 12:00pm

### COGNITIVE COMPUTING: NEUROSCIENCE, SUPERCOMPUTING, NANOTECHNOLOGY

Room: 20AB

### **DHARMENDRA S. MODHA**

IBM Research - Almaden, San Jose, CA

#### **SUMMARY:**

The ultimate goal of the DARPA SyNAPSE project is to build brain-like cognitive computing chips that scale to human cortex by moving beyond the von Neumann architecture and become the brains behind IBM's Smarter Planet vision. The project leverages nanotechnology, supercomputing, and neuroscience and is a collaboration of four universities (Cornell, Columbia, Wisconsin-Madison, and UC Merced) and five IBM sites (Almaden, Yorktown, EFK, BTV, and IRL).

### BIO:

**Dr. Dharmendra S.** Modha is founding manager of the Cognitive Computing group at IBM's Almaden Research Center. Currently, he is the Principal Investigator for DARPA SyNAPSE team of IBM Research - Almaden, IBM Research - Watson, University of Wisconsin-Madison, Cornell University, Columbia University, and University of California at Merced. Most recently, his group performed cortical simulations at scale of cat cerebral cortex (1 billion neurons, 10 trillion synapses) only 100x slower than real-time on a 147,456 processor BlueGene/P supercomputer. This work received the 2009 ACM's Gordon Bell Prize. In 2010, his group compiled, visualized, and analyzed the largest long-distance network currently in existence of the Macaque monkey brain.

His research has had significant practical impact on IBM's businesses. At IBM, he has won the Pat Goldberg Memorial Best Paper award (twice), an Outstanding Innovation Award, an Outstanding Technical Achievement Award, and Communication Systems Best Paper Award. He holds 29 US patents, and is currently an IBM Master Inventor. In 2010, he was elected to the IBM Academy of Technology.

He has authored over 50 publications in international journals and conferences. He is a Fellow of IEEE and a member of AAAS, ACM, and SfN.

Dr. Modha holds a B.Tech. in Computer Science and Engineering from IIT Bombay and a Ph. D. in Electrical and Computer Engineering from UCSD.

## MANAGEMENT DAY

**Additional Registration Fees apply**

Tuesday, June 7 10:30am - 6:30pm

Room: 32AB

### Organizer:

Yervant Zorian - Synopsys, Inc., Fremont, CA

The DAC 2011 Management Day provides managers with timely information to help them make decisions where business and technology intersect. This is a unique opportunity for managers to gain insights from their peers in the industry.

Today's complex SOCs require different types of optimizations and the adoption of emerging solutions to meet such requirements. Optimizing for volume production, low power, and shrinking sizes necessitates accurate trade-off analysis and technical/business decision-making by management. Also, moving to new semiconductor technology nodes, such as 22nm or 28nm, can significantly affect the choices of suppliers. The Management Day sessions will discuss these changing needs and present corresponding management decision criteria that allow managers to make the right choices from a pool of alternate options for flows, methodologies, and suppliers.

The Management Day is comprised of three sessions. The first two sessions will feature presentations by managers representing independent device manufacturers (IDMs), fab-light ASIC providers, foundries, and fabless companies. Senior managers of today's most complex nanometer chips – from Intel, Samsung, Global Foundries, ST Microelectronics, Qualcomm, and other leading companies – will discuss the latest and emerging solutions, along with their economic impact. The third session will be a panel to involve the presenters and the audience in an open brainstorming discussion.

### **SESSION 1: DECISION MAKING FOR COMPLEX ICS**

### 10:30am - 12:00pm

#### **Session Chair:**

Rich Valera - Needham & Co., San Francisco, CA

Moving to new semiconductor technology nodes for complex ICs can significantly affect the choices of design flow, methodologies and suppliers. This session will cover the challenges of complex chip design and present corresponding management decision criteria that allow managers to make the right choices from a pool of alternate options. This session feature presentations by managers representing independent device manufacturers (IDMs), fab-less ASIC providers, and fabless companies.

#### Speakers

Sunil Shenoy - Vice President, Digital Enterprise Group, Intel Corp., Hillsboro, OR Kee Sup Kim - Vice President Design Technology, Samsung, Yongin-City, Republic of Korea Naveed Sherwani - President, Co-founder & CEO, Open-Silicon Inc., Milpitas, CA

#### SESSION 2: TRADE-OFFS AND CHOICES FOR EMERGING SOCS

### 2:00 - 4:00pm

### Session Chair:

Brian Fuller - EE Times

Today's emerging SOCs require multiple types of optimizations and the adoption of advanced solutions to meet stringent design requirements. Optimizing for volume production, low power, and shrinking sizes necessitates accurate trade-off analysis and technical/business decision-making by management. This session will feature senior managers of today's most complex nanometer chips.

#### Speakers

Philippe Magarshack - R&D Group Vice President & GM, ST Microelectronics, Crolles, France

Kevork Keechichian - Vice President Engineering, Qualcomm CDMA Technologies, San Diego, CA

Robert Madge - Director, Design Enabled Manufacturing, GLOBALFOUNDRIES, Milpitas, CA

Magdy Abadir, Raj Raina - Director, Design Automation & Vendor Relations, Freescale Semiconductor, Austin, TX

### SESSION 3: PANEL: CLOUD COMPUTING (HELD NEXT DOOR IN ROOM 33AB)

### 4:00 - 6:30pm

### Session Chair:

Raul Camposano - Physware, Inc., Mountain View, CA

### Session Organizer:

Andreas Kuehlmann - Coverity, Inc., San Francisco, CA

This panel is preceded by a 30 minute tutorial on effective use of the cloud by Amazon's Peter DeSantis.

Cloud computing is THE buzz word today in the software industry. So how and when will cloud computing affect EDA and IC design? Immediate concerns looming on the horizon are security, the transfer of large data sets, and licensing models. This panel, representing a broad set of design and EDA constituents, will examine cloud computing's many implications for the IC design ecosystem.

#### Speakers

Peter DeSantis - Amazon.com, Inc., Seattle, WA John Chilton - Synopsys, Inc., Mountain View, CA John Bruggeman - Cadence Design Systems, Inc., San Jose, CA Greg Gottesman - Madrona Venture Group, Inc., Seattle, WA Mojy Chian - GLOBALFOUNDRIES, Milpitas, CA Carl Anderson - IBM Corp., Austin, TX

## **ESS EXECUTIVE DAY**

### Wednesday, June 8

9:00am - 5:30pm

Room: 32AB

### Organizer:

Yervant Zorian - Synopsys, Inc., Fremont, CA

New for this year's DAC is the focus on Embedded Systems and Software (ESS). The hardware and software design convergence and interdependence in today's complex embedded systems continues to increase. The ESS Executive Day provides managers with timely information to help them make decisions where business and technology in this increasingly important domain intersect. This is a unique opportunity for managers to gain insights from their peers in the industry.

IC design engineers, embedded systems designers, embedded software and hardware IP providers, IP integrators, FPGA designers, investors, foundry reps, and the media will be on hand in this new forum to hear from market leaders and to network with each other. The ESS Executive Day is a day-long track of sessions dedicated to bringing industry stakeholders together in one room to shed light on where system design is headed. The day is comprised of presentations from leading industry executives representing the above sectors.

Presenters will focus on optimization of embedded and application-domain specific operating systems, system architecture for future embedded products, application-specific architectures based on embedded processors and technical/business decision making by program developers. They will cover the state-of-the-art solutions for embedded software and systems and complex chips. Such solutions often require tight collaboration between diverse players in this ecosystem. Moving to new levels of complexity can significantly affect the choices of suppliers. The new ESS Executive Day provides a unique opportunity to foster discussions that address all aspects of the embedded development ecosystem.

### **SESSION 1:**

9:00 - 10:30am

#### Speakers:

Ivo Bolsens - Senior VP and CTO, Xilinx, Inc., San Jose, CA Misha Burich - Senior VP Research and Development, Altera Corp., San Jose, CA John Goodenough - VP Design Technology, ARM, Ltd., Cambridge, United Kingdom Joachim Kunkel - Senior VP, Synopsys, Mountain View, CA

### **SESSION 2:**

2:00 - 3:30pm

### Speakers:

John Bruggeman - Chief Marketing Officer, Cadence Design Systems, Inc., San Jose, CA Sami Issa - Executive Director, Advanced Technology Investment Company, LLC, United Arab Emirates Gabriele Saucier - President and CEO, Design and Reuse, Grenoble, France

### **SESSION 3:**

4:00 - 5:30pm

#### Speakers:

Simon Bloch - VP and General Manager, Mentor Graphics Corp., San Jose, CA Ron Collett - President and CEO, Numetrics, Cupertino, CA Grant Martin - Cheif Scientist, Tensilica, Inc., Santa Clara, CA

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 33ABC

Room: 29AB

Room: 29CD

Tuesday, June 7 10:30am - 12:00pm

**Embedded Systems and Software**

### **PANEL: HACKERS AND ATTACKERS: HOW SAFE IS YOUR EMBEDDED DESIGN?**

### Chair(s):

Ted Vucurevich - Slightly Sharp Enterprises, Atherton, CA

### Organizer(s):

Farinaz Koushanfar - Rice Univ., Houston, TX Todd Austin - Univ. of Michigan, Ann Arbor, MI

#### Speaker(s):

Divya Arora - Intel Corp., Santa Clara, CA Hovav Shacham - Univ. of California at San Diego, La Jolla, CA Igor Markov - Univ. of Michigan, Ann Arbor, MI Jesus Molina - Fujitsu, Santa Clara, CA Kevin Fu - Univ. of Massachusetts, Amherst, MA

We daily entrust embedded devices with our most sensitive information and literally our lives - from smart phones and online banking to critical medical devices such as pacemakers. All this makes embedded systems a delicious target for online attacks and malicious code hackers. Come hear embedded security experts discuss both the growing risks and the emerging tools and methodologies for embedded designers.

Tuesday, June 7 10:30am - 12:00pm

**Embedded Systems and Software**

### SPECIAL SESSION: DESIGN METHODS AND TRENDS FOR AUTOMOTIVE ARCHITECTURES

### Chair(s):

Marco di Natale - Scuola Superiore Sant'Anna, Pisa, Italy Jörg Henkel - Karlsruher Institut für Technologie, Karlsruhe, Germany

### Organizer(s):

Jürgen Teich - Friedrich-Alexander-Universität Samarjit Chakraborty - Technische Univ. München, Munich, Germany

How many embedded processors can you find in your BMW 7 series or in your Tahoe Hybrid? How many millions of lines of code do these embedded processors run? How do these processors communicate? The behavior of today's automobiles, from engine to climate control, is governed by embedded electronics. Current and future requirements for distributed driver assistance and infotainment applications overstrain classic E/E (Electrical/Electronics) architectures and, in particular, their communication infrastructure. This session presents opportune design methods and trends for future automotive network architectures. The talks in this session present novel design concepts for heterogeneous automotive networks that include Ethernet and FlexRay with a focus on challenges, constraints, and realizations.

2.1 Application and Realization of Gateways Between Conventional Automotive and IP/Ethernet-Based Networks

Josef Nöbauer, Helge Zinner, Thomas Gallner - Continental Automotive GmbH, Regensburg, Germany Jochen Seitz - Technische Universität Ilmenau, Ilmenau, Germany

Thomas Waas - Hochschule Regensburg, Regensburg, Germany

2.2 Challenges in a Future IP/Ethernet-Based, In-Car Network for **Real-Time Applications**

Hyung-Taek Lim, Daniel Herrscher - BMW Group Research and Technology, Munich, Germany Lars Völker - BMW Group, Munich, Germany

2.3 Rigorous Model-Based Design and Verification

Flow for In-Vehicle Software

S. Ramesh, Ambar Gadkari - India Science Lab., General Motors Global R&D, Bangalore, India

Tuesday, June 7 10:30am - 12:00pm

**Embedded Systems and Software**

### PERFORMANCE AND RELIABILITY OF FLASH MEMORY SYSTEMS

### Chair(s):

Chang-Gun Lee - Seoul National Univ., Seoul, Republic of Korea

This session presents recent advances in performance and reliability enhancement for flash memory systems. The first paper proposes several novel techniques for improving performance of multi-level cell flash memory. The second paper proposes an approach to write buffer management for improving performance by balancing the two flash-translation-layer strategies of logging and plugging. The third paper presents a version-based strategy for enhancing reliability of flash memory while minimizing the overhead in memory space. The fourth paper characterizes the behavior of flash memories during power failure, which can be a base for future research on enhancing power-related reliability of flash memory systems.

3.1 MNFTL: An Efficient Flash Translation Layer for **MLC NAND Flash Memory Storage Systems**

Zhiwei Qin, Yi Wang, Duo Liu, Zili Shao - The Hong Kong Polytechnic Univ., Kowloon, Hong Kong Yong Guan - Capital Normal Univ., Beijing, China

3.2 Plugging Versus Logging: A New Approach to Write Buffer Management for Solid-State Disks

Li-Pin Chang, You-Chiuan Su - National Chiao Tung Univ., Hsinchu, Taiwan

3.3 A Version-Based Strategy for Reliability Enhancement of Flash File Systems

Pei-Han Hsu, **Po-Chun Huang**, Tei-Wei Kuo - *National Taiwan Univ.*, *Taipei, Taiwan* Yuan-Hao Chang - *National Taipei Univ.* of Technology, Taipei, Taiwan David Hung-Chang Du - *Univ.* of Minnesota, Minneapolis, MN

3.4 Understanding the Impact of Power Loss on Flash Memory Hung-Wei Tseng, Laura M. Grupp, Steven J. Swanson - Univ. of California at San Diego, La Jolla, CA

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 30C

Room: 31AB

Room: 31C

Tuesday, June 7 10:30am - 12:00pm

**Low-Power Design**

### SYSTEM-LEVEL POWER MANAGEMENT

### Chair(s):

Daniel Gajski - Univ. of California, Irvine, CA

The best opportunity for power savings is at the system level. The papers in this session focus on system-level power management techniques for creating power-efficient designs. The first paper focuses on a system workload predictor model for reducing energy consumption, and is followed by a paper describing an integrated power methodology for analyzing multicore SOC designs. The third paper in the session outlines a dynamic voltage scaling technique for reducing the power usage for an OLED display while still providing high quality images. The session concludes with a paper on a novel DRAM/PRAM approach for memory. 4.1 Deriving a Near-Optimal Power Management Policy Using Model-Free Reinforcement Learning and Bayesian Classification Yanzhi Wang, Qing Xie, Massoud Pedram - Univ. of Southern California, Los Angeles, CA

Ahmed C. Ammari - INSAT, Tunis Cedex, Tunisia

4.2 Power Depot: Integrating IP-Based Power Modeling with ESL Power Analysis for Multicore SOC Designs

Chen-Wei Hsu, Jia-Lu Liao, Chia-Chien Weng, Shi-Yu Huang - National Tsing Hua Univ., Hsinchu, Taiwan Shan-Chien Fang - TinnoTek Inc., Hsinchu, Taiwan Wen-Tsan Hsieh, Jen-Chieh Yeh - Industrial Technology Research Institute,

Hsinchu, Taiwan

4.3 Dynamic Voltage Scaling of OLED Displays

Donghwa Shin, Younghyun Kim, Naehyuck Chang - Seoul National Univ., Seoul, Republic of Korea

Massoud Pedram - Univ. of Southern California, Los Angeles, CA 4.4 Power Management of Hybrid DRAM/PRAM-Based Main Memory

Hyun Sun Park, Sungjoo Yoo, Sunggu Lee - Pohang Univ. of Science and Technology, Pohang, Republic of Korea

Tuesday, June 7 10:30am - 12:00pm

**DFM** and the Manufacturing Interface

### **DESIGN FOR MANUFACTURABILITY**

### Chair(s):

Charles Chiang - Synopsys, Inc., Mountain View, CA

This session looks into recent DFM topics. The first paper evaluates the importance of design rules. The second paper looks into self-aligned double-patterning decomposition along with hotspot detection. The third paper develops variability models for standard cells. The final paper develops a synthesis methodology for layouts with regular fabrics.

5.1 To DFM or Not to DFM?

Wing Chiu Tam, Shawn Blanton - Carnegie Mellon Univ., Pittsburgh, PA

5.2 Self-Aligned Double-Patterning Decomposition for Overlay Minimization and Hot Spot Detection

Hongbo Zhang, Yuelin Du, Martin D. F. Wong - Univ. of Illinois at Urbana-Champaign, Urbana, IL

Rasit O. Topaloglu - GLOBALFOUNDRIES, Santa Clara, CA

5.3 Statistical Characterization of Standard Cells Using Design of Experiments with Response Surface Modeling

Miguel Miranda, Philippe Roussel, Lucas Brusamarello - IMEC, Leuven, Belgium Gilson Wirth - Univ. Federal do Rio Grande do Sul, Porto Alegre, Brazil

5.4 Physical Synthesis onto a Layout Fabric with Regular Diffusion and Polysilicon Geometries Nikolai Ryzhenko, Steven Burns - Intel Corp., Hillsboro, OR

Tuesday, June 7 10:30am - 12:00pm

Low-Power Design

### THERMAL MANAGEMENT AND MODELING FOR INTEGRATED CIRCUITS

### Chair(s):

Ayse Coskun - Boston Univ., Boston, MA

The papers in this session address thermal considerations for integrated circuits. The session starts with two papers that present novel dynamic thermal management techniques for microprocessors. The first paper presents a technique for inserting idle cycles for thermal control. The second paper uses a machine-learning based technique for voltage and frequency control that is effective for multimedia applications. The third paper presents a technique to improve power models using post-silicon IR analysis, and the last paper presents a computationally efficient metric that correlates with temperature and is used for floorplan optimization.

6.1 Dimetrodon: Processor-Level Preventive Thermal Management via Idle Cycle Injection

Peter D. Bailis, Sanjay Gandhi, David Brooks, Margo Seltzer - Harvard Univ., Cambridge, MA

Vijay Janapa Reddi - Advanced Micro Devices, Inc., Cambridge, MA

6.2 Dynamic Thermal Management for Multimedia

Applications Using Machine Learning

Yang Ge, Qinru Qiu - SUNY Binghamton, Vestal, NY

6.3 Improved Post-Silicon Power Modeling Using AC Lock-In Techniques Abdullah N. Nowroz, Sherief Reda - Brown Univ., Providence, RI Gary Woods - Rice Univ., Houston, TX

6.4 Thermal Signature: A Simple Yet Accurate Thermal Index for Floorplan Optimization

Jaeha Kung, Inhak Han, Youngsoo Shin - KAIST, Daejeon, Republic of Korea Sachin S. Sapatnekar - Univ. of Minnesota, Minneapolis, MN

www.dac.com

15

### BEST PAPER NOMINEES ARE DENOTED IN GREEN

Room: 33ABC

Room: 29AB

Room: 29CD

Tuesday, June 7 2:00 - 3:30pm

Low-Power Design

### PANEL: CRYSTAL BALL ON LOW POWER: LIMITING TRENDS AND STRATEGIC SOLUTIONS

#### Chair(s):

Dennis Sylvester - Univ. of Michigan, Ann Arbor, MI

#### Organizer(s):

Andrew B. Kahng - Univ. of California at San Diego, La Jolla, CA Nagaraj NS - Texas Instruments, Inc., Dallas, TX

#### Speaker(s):

Jan Rabaey - Univ. of California, Berkeley, CA

Ed Huijbregts - Magma Design Automation, Inc., Eindhoven, The Netherlands S Balajee - Texas Instruments, Inc., Bangalore, India

Stalagee - Texas Instruments, Inc., Bangalore, India

K.S. Kim - Samsung, Yongin, KR

Vivek De - Intel Corp., Hillsboro, OR

Matt Severson - Qualcomm, Inc., San Diego, CA

Wilfried Haensch - IBM T.J. Watson Research Ctr., Yorktown Heights, NY

This panel addresses the entire low-power picture to determine who ultimately is responsible for meeting the low-power system needs. Device engineers could once again save the day. Or, maybe, design and EDA must step up and shoulder the burden. Others insist that system architecture and software solutions will ultimately solve the looming power crisis. The panel will shed light on key technology limits, system needs, and potential solutions.

Tuesday, June 7 2:00 - 3:30pm

**Bio Design Automation**

### **SPECIAL SESSION:** DESIGN AND SYNTHESIS OF BIOLOGICAL CIRCUITS

#### Chair(s):

Douglas Densmore - Boston Univ., Boston, MA Mark Horowitz - Stanford Univ., Stanford, CA

#### Organizer(s):

Smita Krishnaswamy - Columbia Univ., New York, NY Xiling Shen - Cornell Univ., Ithaca, NY

With the growing complexity of synthetic biological circuits, robust and systematic methods are needed for design and test. Leveraging lessons learned from the semiconductor and design automation industries, synthetic biologists are starting to adopt computer aided design and verification software with some success. However, due to the great challenges associated with designing synthetic biological circuits, this nascent approach has to address many problems not present in electronic circuits. In this session, three leading synthetic biologists will share with us how they have developed software tools to help design and verify their synthetic circuits, the unique challenges they faced, and their insight into the next generation of tools for synthetic biology.

8.1 Scalable Parts Families, Context, and Computational

**Design for Gene Expression Engineering** Adam Arkin - Univ. of California, Berkeley, CA

8.2 Gene and Cellular Circuit Design

Chris Voigt - Univ. of California, San Francisco, CA

8.3 A Verifying Compiler for DNA Chemical Reaction Networks

Erik Winfree, Seung Woo Shin - California Institute of Technology, Pasadena, CA

Tuesday, June 7 2:00 - 3:30pm

**Embedded Systems and Software**

### **SWEET STREAMS, EMBEDDED IN MULTICORES**

### Chair(s):

Luca Carloni - Columbia Univ., New York, NY

This session begins with a presentation of work on modeling streaming applications with runtime parameters through Parameterized Polyhedral Process Networks including an evaluation of the overhead introduced by parameterization. We will then hear about work on compiling stream programs onto multicore systems with scratchpad memory through retiming that maximizes throughput under memory contraints. The accions applications with work are improving CPCPUL applications. constraints. The session continues with work on improving GPGPU application performance through memory access analysis. The final presentation is on improving soft error-aware, low-power scheduling through recursive Monte Carlo state space exploration of task execution times.

9.1 Modeling Adaptive Streaming Applications with Parameterized Polyhedral Process Networks

Jiali Teddy Zhai, Hristo Nikolov, Todor Stefanov - Leiden Univ., Leiden, The Netherlands

9.2 Compilation of Stream Programs onto Scratchpad Memory-Based Embedded Multicore Processors Through Retiming Weijia Che, Karam S. Chatha - Arizona State Univ., Tempe, AZ

9.3 CuMAPz: A Tool to Analyze Memory Access Patterns in CUDA Yooseong Kim, Aviral Shrivastava - Arizona State Univ., Tempe, AZ

9.4 SEAL: Soft Error-Aware, Low-Power Scheduling by Monte Carlo State Space Under the Influence of Stochastic Spatial and Temporal Dependencies

Nabeel Iqbal, Muhammad Adnan Siddique, Jörg Henkel - Karlsruher Institut für Technologie, Karlsruhe, Germany

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 30C

Room: 31AB

Room: 31C

Tuesday, June 7 2:00 - 3:30pm

Synthesis and FPGA

### LATE FLOW OPTIMIZATION AND RECTIFICATION

### Chair(s):

Andreas Kuehlmann - Coverity, Inc., San Francisco, CA

Initial synthesis is rarely the final implementation. In this session, we examine ways that designs can be improved or fixed either late in the flow, or after fabrication. The first paper presents a unifying methodology for fixing both timing and functional issues. The second paper uses multiple passes of partial rectification to fix multiple errors efficiently. The third paper presents theoretical complexity results on the multi-domain clock skew scheduling problem, as well as improved heuristics. The final paper examines techniques to optimize circuits utilizing timing speculation by reducing timing-suspicious flip flops and improving the padding of short paths.

10.1 Simultaneous Functional and Timing ECO Iris Hui-Ru Jiang - *National Chiao Tung Univ.*, *Hsinchu, Taiwan* **Hua-Yu Chang**, Yao-Wen Chang - *National Taiwan Univ.*, *Taipei, Taiwan*

10.2 Interpolation-Based Incremental ECO Synthesis for Multi-Error Logic Rectification

Kai-Fu Tang, Chi-An Wu, Po-Kai Huang, Chung-Yang (Ric) Huang - National Taiwan

10.3 Optimal Multi-Domain Clock Skew Scheduling Li Li, Yinghai Lu, Hai Zhou - Northwestern Univ., Evanston, IL

10.4 Resynthesis for Cost-Efficient, Circuit-Level Timing Speculation Yuxi Liu, Feng Yuan, Qiang Xu - The Chinese Univ. of Hong Kong, Shatin, Hong Kong

Tuesday, June 7 2:00 - 3:30pm

**Physical Design**

### **ROUTING REVIVED**

### Chair(s):

Li Zhuo - IBM Corp., Austin, TX

This session proposes new techniques in routing. The first paper presents an optimal algorithm for constructing rectilinear Steiner minimum trees with rectilinear-shaped obstacles. The second paper deals with complex pin access during detailed routing. The third paper is on optimal layer assignment for PCB escape routing, and the last paper proposes a distributed algorithm for layout processing.

11.1 An Exact Algorithm for the Construction of Rectilinear Steiner Minimum Trees Among Complex Obstacles

Tao Huang, Evangeline F. Y. Young - The Chinese Univ. of Hong Kong,

Shatin, Hong Kong

11.2 Gridless Pin Access in Detailed Routing Tim Nieberg - Universität Bonn, Bonn, Germany

11.3 An Optimal Algorithm for Layer Assignment of Bus Escape Routing on PCBs

Qiang Ma, Martin D. F. Wong - Univ. of Illinois at Urbana-Champaign, Urbana, IL Evangeline F. Y. Young - The Chinese Univ. of Hong Kong, Shatin, Hong Kong

11.4 A Distributed Algorithm for Layout Geometry Operations Kai-Ti Hsu, Yu-Chuan Pi, Tsung-Yi Ho - National Cheng Kung Univ., Tainan City, Taiwan Subarna Sinha, Charles Chiang - Synopsys, Inc., Mountain View, CA

Tuesday, June 7 2:00 - 3:30pm

Interconnect and Reliability

### IT'S ALL IN THE MODELS...

### Chair(s):

Eric Keiter - Sandia National Laboratories, Albuquerque, NM

Papers in this session emphasize the importance of proper modeling of the physical properties of systems. Good models capture relevant behavior accurately and can be efficiently generated and evaluated, enabling analysis of performance, yield, or reliability.

The first three papers focus on model approaches to address manufacturing and operating conditions or process variations. The papers cover issues ranging from mechanical reliability, modeling spatial variations on an IC, and improving failure rate estimation. The final two papers address the efficiency of model generation and evaluation by employing careful statistical analysis as well as appropriate compressed representations.

12.1 TSV Stress-Aware, Full-Chip Mechanical Reliability **Analysis and Optimization for 3-D IC**

Sung Kyu Lim, **Moongon Jung** - Georgia Institute of Technology, Atlanta, GA Joydeep Mitra, David Z. Pan - Univ. of Texas, Austin, TX

12.2 Hybrid Modeling of Non-Stationary Process Variations Eva Dyer, Mehrdad Majzoobi, Farinaz Koushanfar - Rice Univ., Houston, TX

12.3 Efficient SRAM Failure Rate Prediction via Gibbs Sampling Xin Li, Changdao Dong - Carnegie Mellon Univ., Pittsburgh, PA

12.4 Direct Matrix Solution of Linear Complexity for Surface Integral Equation-Based Impedance Extraction of High Bandwidth Interconnects Wenwen Chai, Dan Jiao - Purdue Univ., West Lafayette, IN

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Tuesday, June 7 4:00 - 6:00pm

**Emerging Technologies**

Room: 33ABC

Room: 29AB

Room: 29CD

### PANEL: CLOUD COMPUTING AND EDA FORECAST: SUNNY SKIES OR STORM CLOUDS AHEAD?

#### Chair(s):

Raul Camposano - Physware, Inc., Mountain View, CA

#### Organizer(s):

Andreas Kuehlmann - Coverity, Inc., San Francisco, CA

#### Speaker(s):

Peter DeSantis - Amazon.com, Inc., Seattle, WA John Chilton - Synopsys, Inc., Mountain View, CA John Bruggeman - Cadence Design Systems, Inc., San Jose, CA Greg Gottesman - Madrona Venture Group, Inc., Seattle, WA Mojy Chian - GLOBALFOUNDRIES, Milpitas, CA Carl Anderson - IBM Corp., Austin, TX

This panel is preceded by a 30 minute tutorial on effective us of the cloud by Amazon's Peter DeSantis.

Cloud computing is THE buzz word today in the software industry. So how and when will cloud computing affect EDA and IC design? Immediate concerns looming on the horizon are security, the transfer of large data sets, and licensing models. This panel, representing a broad set of design and EDA constituents, will provide the properties of the constituents. examine cloud computing's many implications for the IC design ecosystem.

Tuesday, June 7 4:00 - 6:00pm

**Emerging Technologies**

### **SPECIAL SESSION: KILLER APPS FOR 3-D ICS?**

### Chair(s):

Lei He - Univ. of California, Los Angeles, CA

### Organizer(s):

Sung Kyu Lim - Georgia Institute of Technology, Atlanta, GA

3-D IC technology has promised a great deal for several years - but is it ready to move from being the technology of tomorrow to that of today? The NRE costs associated with 3-D design, manufacturing, and test are steep, and cannot be justified without killer apps that provide the appropriate ROI. This session features four talks from industry experts on their view of apps that will help move 3-D towards the mainstream. The topics covered in this session include design challenges and opportunities, processor/memory issues, and heterogeneous 3-D integration, including systems that integrate optical and RF interconnects.

14.1 Design, CAD, and Technology Challenges for **Future Processors: 3-D Perspectives**

Jeff Burns, Gary Carpenter, Eren Kursun, Ruchir Puri, **James Warnock**, Michael Scheuermann - *IBM Corp.*, *Yorktown Hts*, *NY*

14.2 3-D Heterogeneous System Integration: Application Driver for 3-D Technology Development

Eric Beyne, Pol Marchal, Geert Van Der Plas - IMEC, Leuven, Belgium

14.3 3D Integration for Energy Efficient System Design Shekhar Borkar - Intel Corp., Hillsboro, OR

14.4 Applications Driving 3-D Integration and **Corresponding Manufacturing Challenges** Rasit Topaloglu - GLOBALFOUNDRIES, Milpitas, CA

Tuesday, June 7 4:00 - 6:00pm

**Embedded Systems and Software**

### **TOWARDS EMBEDDED SYSTEMS WE CAN TRUST:** FROM MODELS TO GATES

### Chair(s):

Nachiketh Potlapally - Intel Corp., Princeton, NJ

This session deals with the trustworthiness of embedded systems from abstract models down to gates. The first paper presents a novel test-case generation technique using formal concept analysis. The second paper presents a design flow for software to mitigate the power side channel. The third paper presents a simulation for estimating the impact of TPM on the performance of applications. The fourth paper proposes a prototype architecture for a low-cost and fast, public, and physically unclonable function. The next paper shows how variable supply voltage techniques can be used to detect three types of IC trojan attacks. The final paper demonstrates the application of gate-level information flow tracking to provide a method for testing information flows in two common bus protocols.

#### 15.1 Test-Case Generation for Embedded Simulink via Formal Concept Analysis

Nannan He, Daniel Kroening - Oxford Univ., Oxford, United Kingdom Philipp Ruemmer - Uppsala Univ., Uppsala, Sweden

15.2 A First Step Towards Automatic Application of Power Analysis Countermeasures

Ali Galip Bayrak, Paolo lenne - Ecole Polytechnique Fédérale de

Lausanne, Switzerland

Francesco Regazzoni, Francois-Xavier Standaert - Univ. Catholiqué de Louvain,

Baaschtnech, Belgium

Philip Brisk - Univ. of California, Riverside, CA

15.3 TPM-SIM: A Framework for Performance **Evaluation of Trusted Platform Modules**

Jared Schmitz, Jason Loew, Jesse Elwell, Dmitry Ponomarev, Nael Abu-Ghazaleh - SUNY Binghamton, Binghamton, NY

15.4 Differential Public, Physically Unclonable **Functions: Architecture and Applications**

Miodrag Potkonjak, Sheng Wei, Saro Meguerdichian, Ani Nahapetian - *Univ. of California, Los Angeles, CA*

15.5 Integrated Circuit Security Techniques Using Variable Supply Voltage Miodrag Potkonjak, Sheng Wei - Univ. of California, Los Angeles, CA

15.6 Information Flow Isolation in I2C and USB

Jason Oberg, Ali U. Irturk, Ryan Kastner - Univ. of California at San Diego

La Jolla, CA

Wei Hu - Northwestern Polytechnical Univ., Xian, China

Mohit Tiwari, Timothy Sherwood - Univ. of California, Santa Barbara, CA

**BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 30C

Room: 31AB

Room: 31C

Tuesday, June 7 4:00 - 6:00pm

System-Level Design

### SPECIAL SESSION: **EMBEDDED MULTIPROCESSOR SOFTWARE SYNTHESIS**

Peter Marwedel - Technische Univ. Dortmund, Dortmund, Germany Daniel Gajski - Univ. of California, Irvine, CA

### Organizer(s):

Andreas Gerstlauer - Univ. of Texas, Austin, TX Christian Haubelt - Friedrich-Alexander-Universität Erlangen-Nürnberg, Nuremberg, Germany

Future embedded systems will consist of tens to hundreds of heterogeneous programmable cores. How do we optimally program them? The synthesis of optimized software implementations that respect tight constraints imposed by operating environments from high-level, abstract input models becomes very attractive. This session will present state-of-the-art approaches for embedded multi-processor software development, with topics ranging from the search for novel temporal abstractions and programming models to complete environments for automatic synthesis of efficient and performance-, power- and temperature-optimized software across heterogeneous SOCs, including perspectives from both practitioners in industry as well as academic researchers. 16.1 CIRUS: A Scalable Modular Architecture for Reusable Drivers Bratin Saha - Intel Corp., Santa Clara, CA

16.2 Programming Challenges and Solutions for Multiprocessor SOCs: An Industrial Perspective Pierre G. Paulin - STMicroelectronics, Ottawa, ON, Canada

16.3 Thermal-Aware System Analysis and Software Synthesis for Embedded Multiprocessors

Lothar Thiele, Lars Schor, Hoeseok Yang, Iuliana Bacivarov - Eidgenössische Technische Hochschule Zürich, Zurich, Switzerland

16.4 Temporal Isolation on Multiprocessing Architectures Dai Bui, Edward A. Lee, Isaac Liu, Jan Reineke - Univ. of California, Berkeley, CA Hiren Patel - Univ. of Waterloo, Waterloo, ON, Canada

Tuesday, June 7 4:00 - 6:00pm

**General Interest**

### **WILD AND CRAZY IDEAS**

### Chair(s):

Valeria Bertacco - Univ. of Michigan, Ann Arbor, MI

The WACI session showcases wild and crazy, thought-provoking ideas and is intended to promote wild and crazy discussion and debate. This year's presentations include applications of EDA to social networks and internet search, "true" 3-D architectures with vertical transistors, orchestrated flow analysis to benefit ever-changing design teams, binary translation for acceleration on-the-fly, using device aging to improve circuit security, and energy-efficient computing on unreliable platforms. We expect the wild and crazy questions that make the WACI experience complete; the WAClest presentation and the WAClest question will be appropriately recognized!

17.1 Physics-Based, Field-Theoretic Design Automation Tools for Social Networks and Web Search

Vikram Jandhyala - Univ. of Washington, Seattle, WA

17.2 Can We Go Towards True 3-D Architectures?

Pierre-Emmanuel Gaillardon, Haykel Ben-Jamaa, Paul-Henry Morel, Jean-Philippe Noël, Fabien Clermidy - CEA-Leti, Grenoble, France lan O'Connor - École Centrale de Lyon, Lyon, France

17.3 Orchestrated Multi-Level Information Flow Analysis to Understand SOCs

Görschwin Fey - Univ. Bremen, Bremen, Germany

17.4 Dynamic Binary Translation to a Reconfigurable Target for On-the-Fly Acceleration

Phillip J. Kinsman, Nicola Nicolici - McMaster Univ., Hamilton, ON, Canada

17.5 Device Aging-Based Physically Unclonable Functions

Saro Meguerdichian, Miodrag Potkonjak - Univ. of California, Los Angeles, CA

17.6 Significance-Driven Computation On Next-Generation Unreliable Platforms

Georgios Karakonstantis - Swiss Federal Institute of Technology, Lausanne,

Nikolaos Bellas, Christos Antonopoulos, Georgios Tziatzaoulis - Univ. of Thessaly, Vaibhav Gupta, Kaushik Roy - Purdue Univ., West Lafayette, IN

Tuesday, June 7 4:00 - 6:00pm

Analog/Mixed-Signal/RF Design

### ANALOG AND MIXED-SIGNAL DESIGN **IN AN UNCERTAIN WORLD**

### Chair(s):

Trent McConaghy - Solido Design Automation, Inc., Saskatoon, CA

This session hosts recent innovations to combat the noise and variability issues faced in today's analog and mixed-signal circuits. The first two papers propose novel algorithms for simulating thermal, flicker, and random telegraph noise in the time domain. The next two papers focus on ways to ensure stability and performance of nanoscale analog circuits in the presence of process variation. The final two papers present ideas to improve the system reliability and new advances in reconfigurable analog designs.

18.1 MUSTARD: A Coupled, Stochastic-Deterministic, Discrete-Continuous Technique for Predicting the Impact of Random Telegraph Noise on SRAMs and DRAMs

Karthik V. Aadithya, Sriram Venugopalan, Jaijeet Roychowdhury - Univ. of California,

Alper Demir - Koç Univ., Sariyer-Istanbul, Turkey

18.2 Fast, Non-Monte-Carlo Transient Noise Analysis for High-Precision Analog/RF Circuits by Stochastic Orthogonal Polynomials

Fang Gong, Lei He - Univ. of California, Los Angeles, CA Hao Yu - Nanyang Technological Univ., Singapore, Singapore

### 18.3 Automatic Stability Checking for Large, Linear Analog Integrated

Parijat Mukherjee, Peng Li - Texas A&M Univ., College Station, TX G. Peter Fang, Rod Burt - Texas Instruments, Inc., Dallas, TX

18.4 Performance Bound Analysis of Analog Circuits Considering Process Variations

Zhigang Hao, Guoyong Shi - Shanghai Jiao Tong Univ., Shanghai, China Sheldon X.-D. Tan, Ruijing Shen - Univ. of California, Riverside, CA

18.5 Rethinking Memory Redundancy: Optimal Bit Cell Repair for Maximum-Information Storage Xin Li - Carnegie Mellon Univ., Pittsburgh, PA

18.6 Programmable Analog Device Array (PANDA): A Platform for Transistor-Level Analog Reconfigurability Rui Zheng, Jounghyuk Suh, Cheng Xu, Bertan Bakkaloglu, Yu Cao - Arizona State

Univ., Tempe, AZ Nagib Hakim - Intel Corp., Santa Clara, CA

www.dac.com

19

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Wednesday, June 8 9:00 - 10:30am

General Interest Room: 33ABC

### 19 PANEL

## PANEL: EDA RESEARCH: STALLED, DRIVING IN CIRCLES, OR RUNNING OUT OF GAS?

### Chair(s):

William Joyner - Semiconductor Research Corp., Research Triangle Park, NC

### Organizer(s):

Igor Markov - Univ. of Michigan, Ann Arbor, MI

#### Speaker(s):

Robert Brayton - Univ. of California, Berkeley, CA

Philippe Magarshack - STMicroelectronics, Crolles, France

Charles Alpert - IBM Corp., Austin, TX

Rob A. Rutenbar - Univ. of Illinois at Urbana-Champaign, Urbana, IL

Shankar Krishnamoorthy - Mentor Graphics Corp., Fremont, CA

Everyone seems frustrated with the inefficiencies in EDA Research. So who's to blame, and more importantly, who should fix it? One answer is that industry vendors need to take a more active role in supporting research. Or, should researchers focus more on real-world problems instead of generating papers? Come watch as these constituencies defend themselves, and in the end, you'll decide who is wasting gas!

Wednesday, June 8 9:00 - 10:30am

Verification and Test

## SPECIAL SESSION: SCALING AND SECURITY: DOES MORE TRANSISTORS MEAN MORE SECURITY?

#### Chair(s):

Ken Mai - Carnegie Mellon Univ., Pittsburgh, PA

### Organizer(s):

Soha Hassoun - Tufts Univ., Medford, MA

The unprecedented levels of integrated circuit performance, efficiency, and affordability enabled by process technology scaling has led to the pervasive deployment of microelectronic systems. Because these systems routinely store, manipulate, and transmit sensitive data, there is a strong and growing interest in building secure systems. This session discusses how process technology scaling has at once made the design and implementation of secure systems easier and harder. The talks present views of the implications of continued technology scaling for building secure systems and the state-of-the-art in semiconductor reverse engineering.

20.1 Complexity and the Challenges of Securing SOCs

Paul Kocher - Cryptography Research, Inc., San Francisco, CA

20.2 High Performance Energy-Efficient Encryption in the sub-45nm CMOS Era

Ram Krishnamurthy, Sanu Mathew, Farhana Sheikh - Intel Corp., Hillsboro, OR

Room: 29AB

Room: 29CD

20.3 The State-of-the-Art in Semiconductor Reverse Engineering Randy Torrance, Dick James - Chipworks Inc., Ottawa, ON, Canada

Wednesday, June 8 9:00 - 10:30am

System-Level Design

21

### NEED FOR SPEED: SYSTEM-LEVEL ANALYSIS AND DESIGN

### Chair(s):

Luciano Lavagno - Politecnico di Torino, Torino, Italy

This session presents approaches for rapid simulation of multicore systems, design analysis, and performance optimization of maximum temperature and error-detection algorithms. The first two papers address fast parallel simulation for multicore systems by effective configuration of simulation platforms and their scheduling. The third paper addresses statistical performance analysis by correlating transaction models with RTL. The fourth paper effectively extracts design hierarchy modeled by SystemC. The last two papers focus on performance optimization under temperature constraints and for error detection mechanisms.

21.1 A High-Parallelism Distributed Scheduling Mechanism for Multicore Instruction-Set Simulation

Meng-Huan Wu, Peng-Chih Wang, Cheng-Yang Fu, Ren-Song Tsay - National Tsing Hua Univ., Hsinchu, Taiwan

21.2 Simulation Environment Configuration for Parallel Simulation of Multicore Embedded Systems

**Dukyoung Yun**, Jinwoo Kim, Soonhoi Ha - Seoul National Univ., Seoul, Republic of Korea

Sungchan Kim - Chonbuk National Univ., Jeonju, Republic of Korea

21.3 Transaction-Level Statistical Analysis for Efficient Microarchitectural Power and Performance Studies

Eman Copty, Gila Kamhi, Sasha Novakovsky - Intel Corp., Haifa, Israel

21.4 Extracting Behavior and Dynamically-Generated Hierarchy from SystemC Models

Harry Broeders, René van Leuken - Delft Univ. of Technology, Delft, The Netherlands

21.5 Throughput Maximization for Periodic Real-Time Systems Under the Maximal Temperature Constraint

Huang Huang, Gang Quan, Jeffrey Fan - Florida International Univ., Miami, FL Meikang Qiu - Univ. of Kentucky, Lexington, KY

21.6 Performance Optimization of Error Detection Based on Speculative Reconfiguration

Adrian Alin Lifa, Petru Eles, Zebo Peng - Linköping Univ., Linkoping, Sweden

**BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 30C

Room: 31AB

Room: 31C

Wednesday, June 8 9:00 - 10:30am

**Embedded Systems and Software**

### TRENDS IN SYSTEM-LEVEL DESIGN SPACE EXPLORATION AND OPTIMIZATION

Lothar Thiele - Eidgenössische Technische Hochschule Zürich, Zurich, Switzerland

This session consists of six papers covering different aspects of high-level system exploration and optimization. The first four papers address sustainability, extensibility, timing, and reliability issues in application domains such as automotive, multimedia, and mobile applications. The fifth paper proposes techniques for multi-objective design space exploration, and finally the sixth paper deals with system design using emerging memory technologies.

22.1 On the Quantification of Sustainability and Extensibility of FlexRay Schedules

Reinhard Schneider, Dip Goswami, Samarjit Chakraborty - Technische Univ.

München, Munich, Germany Unmesh D. Bordoloi, Petru Eles, Zebo Peng - Linköping Univ., Linkoping, Sweden

22.2 Generalized Reliability-Oriented Energy Management for Real-Time Embedded Applications

Baoxian Zhao, Hakan Aydin - George Mason Univ., Fairfax, VA Dakai Zhu - Univ. of Texas, San Antonio, TX

22.3 Customer-Aware Task Allocation and Scheduling for Multi-Mode MPSOCs

Lin Huang, Rong Ye, Qiang Xu - The Chinese Univ. of Hong Kong, Shatin, Hong Kong

22.4 Symbolic System Synthesis in the Presence of Stringent Real-Time Constraints

Felix Reimann, Michael Glaß, Christian Haubelt, Juergen Teich - Friedrich-Alexander-Universität Erlangen-Nürnberg, Erlangen, Germany

Martin Lukasiewycz - Technische Univ. München, Munich, Germany

22.5 Supervised Design Space Exploration by Compositional Approximation of Pareto Sets

Hung-Yi Liu, Michele Petracca, Luca Carloni - Columbia Univ., New York, NY Ilias Diakonikolas - Univ. of California, Berkeley, CA

22.6 Power-Aware Variable Partitioning for DSPs with Hybrid PRAM and DRAM Main Memory

Tiantian Liu, Yingchao Zhao, Chun Jason Xue, Minming Li - City Univ. of Hong Kong, Kowloon, Hong Kong

Wednesday, June 8 9:00 - 10:30am

Verification and Test

### **VALIDATION AND TEST: THE YIN AND YANG**

### Chair(s):

Shobha Vasudevan - Univ. of Illinois at Urbana-Champaign, Urbana, IL

Experience a true merger of validation and test in this session. The first paper applies efficient debug techniques to industrial designs. The second diagnoses the key causes of intermittent timing failures. The third provides enhanced ATPG efficiency for path-delay faults. Finally, the fourth improves timing failure diagnosis by handling multiple faults when their impact is complicated by clustering.

23.1 TAB-BackSpace: Unlimited-Length Trace Buffers with Zero Additional On-Chip Overhead

Flavio M. de Paula, Alan Hu - Univ. of British Columbia, Vancouver, BC, Canada Amir Nahir, Ziv Nevo, Avigail Orni - IBM Corp., Haifa, Israel

23.2 Testability Driven Statistical Path Selection Jaeyong Chung, Jacob A. Abraham - Univ. of Texas, Austin, TX Jinjun Xiong, Vladimir Zolotov - IBM Corp., Yorktown Hts., NY

23.3 Diagnosing Scan Clock Delay Faults Through Statistical Timing Pruning

Mingjing Chen, Alex Orailoglu - Univ. of California at San Diego, La Jolla, CA

23.4 Diagnosis of Transition Fault Clusters Irith Pomeranz - Purdue Univ., West Lafayette, IN

Wednesday, June 8 9:00 - 10:30am

Low-Power Design

### LEAKAGE POWER OPTIMIZATION

### Chair(s):

David Garrett - Broadcom Corp., Irvine, CA

As the semiconductor industry continues its march down 32nm, leakage power continues to increase its dominance in the total power consumption. This session presents different exciting efforts to lower leakage power. The session starts with a paper that presents a leakage-aware redundancy for reliable subthreshold memories and continues with another that offers a 40nm subthreshold standard cell library, which takes inverse-narrow-width-effect into account. The session process with the property line added requirements and process and process are continued to the property of the propert ends with two papers that propose line-edge roughness aware poly-layout optimization and post sign-off adjustments, respectively. The objective of both papers is to further reduce the leakage power.

24.1 Leakage-Aware Redundancy for Reliable Subthreshold Memories Seokjoong Kim, Matthew Guthaus - Univ. of California, Santa Cruz, CA

24.2 A 40nm Inverse Narrow-Width, Effect-Aware

Subthreshold Standard Cell Library

Jun Zhou - Institute of Microelectronics, Singapore, Singapore Senthil Jayapal - Intel Corp., Penang, Malaysia Ben Busze, Li Huang, **Jan Stuyt** - Holst Centre, Eindhoven, The Netherlands

24.3 Layout-Aware, Line-Edge Roughness Modeling and Poly-Optimization for Leakage Minimization Yongchan Ban, Jae-Seok Yang - Univ. of Texas, Austin, TX

24.4 Post Sign-Off Leakage Power Optimization

Hamed Abrishami, Massoud Pedram - Univ. of Southern California, Los Angeles, CA Jinan Lou - Google, Inc., Mountain View, CA Jeff Qin, Juergen Froessl - Synopsys, Inc., Mountain View, CA

### **BEST PAPER NOMINEES ARE DENOTED IN GREEN**

Room: 33ABC

Room: 29AB

Room: 29CD

Wednesday, June 8 2:00 - 3:30pm

System-Level Design

25

### PANEL: SOFTWARE-HARDWARE VERIFICATION BATTLE: PROTOTYPING VS. EMULATION

### Chair(s):

Bryon Moyer - Techfocus Media, Inc., San Jose, CA

### Organizer(s):

Valeria Bertacco - Univ. of Michigan, Ann Arbor, MI

#### Speaker(s):

Subhasish Mitra - Stanford Univ., Stanford, CA Chris Tice - Cadence Design Systems, Inc., San Jose, CA Avi Ziv - IBM Corp., Haifa, Israel Joachim Kunkel - Synopsys, Inc., Mountain View, CA Raj Yavatkar - Intel Corp., Portland, OR Albert Camilleri - Qualcomm, Inc., San Diego, CA In today's multiprocessor/multicore designs, it is becoming essential to verify software execution before committing to silicon. Some say prototyping is essential - but that could be by virtual prototype or by FPGA. Others say emulation is the way to go. Who is right? Experts from academia and the industry will wrestle with the question to determine the best way to success.

Wednesday, June 8 2:00 - 3:30pm

**DFM** and the Manufacturing Interface

### 26

## SPECIAL SESSION: DESIGN AND TECHNOLOGY AT 14NM NODE: MYTHS AND REALITIES

#### Chair(s):

Geoffrey Yeap - Qualcomm, Inc., San Diego, CA

### Organizer(s):

Ruchir Puri - IBM Corp., Yorktown Hts., NY David Z. Pan - Univ. of Texas, Austin, TX

The semiconductor industry continues to battle the laws of physics on its march towards the next few technology nodes. As we move down this path, what are the design and technology challenges in store for our community? What are the kinds of research problems that we will need to solve? This session is intended to be an eye-opening experience that previews the pain that we may encounter in the 14nm era. The three invited talks will cover topics from lithographyl scaling to new transistor structures to circuit design challenges at 14nm and beyond.

26.1 Lithography at 14nm and Beyond: Choices and Challenges Vivek Singh - Intel Corp., Portland, OR

26.2 New Sub-20nm Transistors - Why and How

Chenming Hu - Univ. of California, Berkeley, CA

26.3 Circuit Design Challenges at the 14nm Technology Node James Warnock - IBM Corp., Yorktown Hts., NY

Wednesday, June 8 2:00 - 3:30pm

**Embedded Systems and Software**

### 27

### **PUNCTUAL SOFTWARE: IT'S ABOUT TIME**

### Chair(s):

Sami Yehia - Thales Group, Palaiseau, France